# Fast Charging Photoflash Capacitor Charger with Wide Range Current Limiter

Won Ho Choi, Woo Kwan Lee, Soo-Won Kim

#### Abstract

The fast charging photoflash capacitor charger with wide range current limiter is presented. By using proposed control logic block and wide range current limiter, the photoflash capacitor charger can reduce charging time and control life of battery for user convenience. The proposed photoflash capacitor charger has 3s charging time at 3.3V battery voltage, 1.2A current limit condition. It is well-suited for portable device application like digital camera, digital video camera, and mobile phone with camera.

Key words: DC-DC converter, Flyback converter, Photoflash capacitor charger, Fast charging time

#### 1. Introduction

It requires high voltage over 300V for flashing the Xenon bulb commonly used in digital camera and mobile phone. For that reason, it requires large photoflash capacitor and charging circuit. Nowadays, the photoflash capacitor charger of micro-controlled flyback converter type is the most popular charging circuit because of its low power and small area characteristic [1]. The most important aspects of this structure are charging time and efficiency. Fast charging time is an advantage that user can have short latency time. And control logic block is the most important block to decide the charging time of the photoflash capacitor charger. To address this issue. various design techniques have been developed to fast transient response and to have high efficiency for flyback converter [2]-[4]. This paper proposes the architecture that the control logic block approaches for fast charging with high efficiency of photoflash capacitor charger. However, for faster charging time, the photoflash capacitor charger must select large peak current of transformer primary side current which

This work is supported by IT R&D Project funded by Korean Ministry of Information and Communications and Nano IP/SoC Promotion Group of Seoul R&BD Program in 2007. And authors thank IDEC (IC Design Education Center) for its assist with providing hardware and software.

gives a bad effect of battery life [5]. So, for user convenience, it can control widely current limiting by using proposed wide range of current limiter.

187

In this paper, section 2 reviews operation of photoflash capacitor charger. Section 3 describes conventional and proposed control logic block. The simulation and the experimental results are shown in section 4. At last, conclusion is shown in section 5 respectively.

## 2. Operation of Photoflash Capacitor Charger

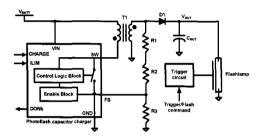

Fig. 1(a) shows the flashlamp circuitry using the photoflash capacitor charger of micro-controlled flyback converter type. This structure consists of transformer, photoflash capacitor, power switch (Power transistor) for primary current control of transformer, control logic block for switching of power switch, enable block for enable and disable of control logic block [6]. Fig. 1(b) shows timing diagram of the photoflash capacitor charger of micro-controlled flyback converter type. The charging operation of the photoflash capacitor charger of micro-controlled flyback converter type is started by a low-to-high signal on the CHARGE pin (A point in timing diagram). When a charging cycle is initiated, the transformer primary side current, I<sub>Primary</sub>, ramps up linearly at a rate determined by the combined effect of the battery voltage, V<sub>BATT</sub>, and the SW node voltage, V<sub>SW</sub>, and the power switch

on-time, t, and the primary side inductance,  $L_{Primary}$ , as shown in equation (1).

When  $I_{Primary}$  reaches the current limit,  $I_{LIM}$ , set by configuring the ILIM pin, the internal power switch is turned off immediately, allowing the energy to be pushed into the photoflash capacitor,  $C_{OUT}$ , from the secondary winding. The output voltage,  $V_{OUT}$ , rises by this repetitious process.

(a) Block diagram

(b) Timing diagram

Fig. 1. Flashlamp circuitry using micro-controlled flyback converter type photoflash capacitor charger.

$$I_{primary} = \frac{1}{L_{primary}} \cdot (V_{BATT} - V_{SW}) \cdot t \tag{1}$$

While the internal power switch is turned off, V<sub>OUT</sub> is sensed by a resistor string, R1 through R3, connected between the anode of the output diode, D1, and ground. This resistor string forms a voltage divider that feeds back to the FB pin.

$$V_{OUT} = \frac{R1 + R2 + R3}{R3} \cdot V_{FB}$$

(2)

Where  $V_{FB}$  is FB node voltage. The resistors must be sized to achieve a desired output voltage. When  $V_{OUT}$  reaches the desired value, the charging process is terminated. And DONEb signal goes low to indicate the completion of the charging process (B point in timing diagram). After then, trigger circuit that operates by flash command discharges  $V_{OUT}$  to the flashlamp (C point in timing diagram). As a result, the flashlamp flashes the light.

## 3. Control Logic Block of Photoflash Capacitor Charger

## 3.1 Conventional Control Logic Block

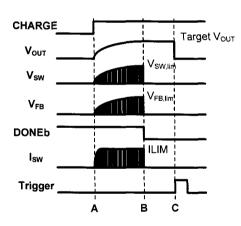

Fig. 2 shows the control logic block of the conventional photoflash capacitor charger [6].

Fig. 2. Conventional control logic block

The feature of the conventional control logic block is as follows. At first, ILIM can be set to 3-level (1.0A, 1.2A, 1.4A) by configuring the ILIM pin (ground, float, Vdd). Lower input current offers the advantage of a longer battery lifetime. In the mean time, the highest current limit is required for faster charging time.

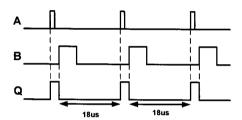

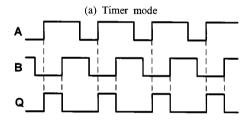

Second, the conventional architecture has two modes (timer mode and fast charging mode) by using ILIM comparator and DCM comparator. Fig. 3 shows the timing diagram of conventional control logic block.

The conventional architecture operates in the timer mode when it begins to charger a completely discharged photoflash capacitor, usually when  $V_{OUT}$  is less than 10 to 20V. Timer mode is fixed to 18 $\mu$ s off-time control. It can be recognized by

lowering initial input charging current as a result of a lower duty cycle, like soft start [7]. As  $V_{OUT}$  rises to more than 10 to 20V, converter operates near the discontinuous boundary, and sensing circuit tracks the fly-back voltage at SW node. As soon as this voltage swings below determined voltage, the internal power switch turns on again, starting the next charging cycle. The process is repeated like this and boosts the voltage to a goal voltage. The conventional architecture has a defect that charging time comes slow by long off-time duration (18 $\mu$ s) in the timer mode.

(b) Fast charging mode

Fig. 3. Timing diagram of conventional control logic block.

## 3.2 Proposed Control Logic Block

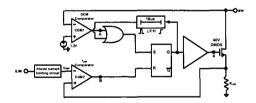

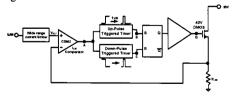

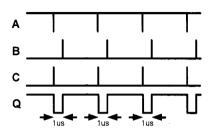

Fig. 4 shows block and timing diagram of proposed control logic clock.

(a) Block diagram

(b) Timing diagram

Fig. 4. Proposed control logic block.

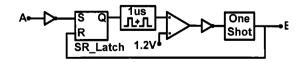

Proposed control logic block operates one mode (fast charging mode) unlike the conventional architecture by taking off DCM comparator. And the proposed architecture puts the up-pulse triggered timer path with down-pulse triggered timer path and adjusted on-off time duration. Fig. 5 shows block diagram of proposed up-pulse and down-pulse triggered timer.

In the proposed architecture, the power switch on-time is decided by  $V_{BATT}$ ,  $L_{Primary}$ , and  $I_{LIM}$ . And the power off-time is decided by delay cell in the up-pulse triggered timer. Equation (3) indicates minimum off-time,  $t_{OFF}$ , for full-discharge of transformer [5].

$$I_{LIM} = \frac{V_{OUT}}{n \cdot L_{primary}} \cdot t_{OFF}$$

(3)

Where n are transformer turns ratio. If n is 10 and  $I_{LIM}$  is 1.2A and  $V_{OUT}$  is 300V and  $L_{Primary}$  is 14 $\mu$ H,  $t_{OFF}$  is 560ns of the calculation. So, up-pulse triggered timer is designed by using 1 $\mu$ s delay cell as it is enough time for the photoflash capacitor to charge delivering voltage from secondary side of transformer. As the result, it can respect fast charging time characteristic of photoflash capacitor charger by faster switching of power switch than conventional architecture.

(a) Up-pulse triggered timer

(b) Down-pulse triggered timer

Fig. 5. Proposed up-pulse & down-pulse triggered timer block diagram.

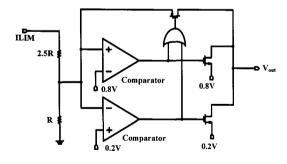

As the importance of the lower power characteristic for digital cameras and mobile phones is being increased day by day, low power photoflash capacitor charger is required. So wide range current limiter is proposed for adjusting low power application. Fig. 6 shows the block diagram of the proposed wide range current limiter.

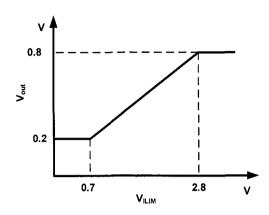

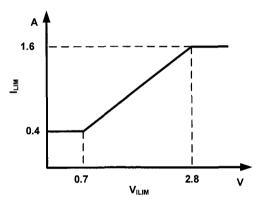

The operation of the wide range current limiter is as follows. The inner comparators decide upper and lower side of current limiting point. And, 2.5R and R are used for preventing the ILIM node noise voltage [8]-[9]. If ILIM node voltage,  $V_{ILIM}$ , is less than 0.7V, the output voltage,  $V_{out}$ , is 0.2V. On the other hand, if  $V_{ILIM}$  is over 2.8V,  $V_{out}$  is 0.8V. If  $V_{ILIM}$  is from 0.7V to 2.8V,  $V_{out}$  has proportional value from 0.2V to 0.8V. Designed  $R_{LIM}$  is  $0.5\Omega$  in figure 4(a). According to Ohm's law, the proposed wide range current limiter can control  $I_{LIM}$  range from 0.4A to 1.6A. Fig. 7 shows  $V_{out}$  and  $I_{LIM}$  as  $V_{ILIM}$  of the proposed wide range current limiter.

Fig. 6. Proposed wide range current limiter block diagram.

(a) Vout vs. VILIM

(b)  $I_{LIM}$  vs.  $V_{ILIM}$  Fig. 7. Proposed wide range current limiter  $V_{out}$  and  $I_{LIM}$  as  $V_{ILIM}$

## 4. Simulation and Experimental Results

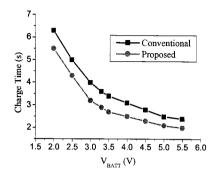

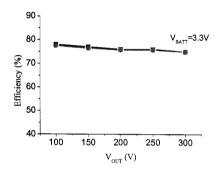

To verify the performance of the photoflash capacitor charger using proposed control logic block and wide range current limiter, the simulation is conducted charging time, efficiency and current limiting range. For comparison, the same simulation is also conducted with the conventional architecture. Fig. 8(a), (b) shows the results of the simulation for charging time and efficiency. The proposed photoflash capacitor charger has faster charging time as similar to conventional structure efficiency.

Figure 8(c) shows the result of the simulation for proposed photoflash capacitor charger current limiting range as  $V_{LIM}$ .

(a) Charging time

(b) Efficiency

1.8-1.6 1.4 1.2 1.0 0.8 T 0.6 0.4 0.2 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5  $V_{LIM}(V)$

(c) Current limiting range

Fig. 8. Simulation results.

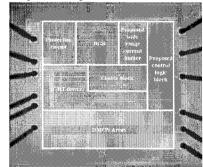

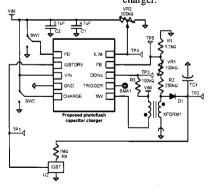

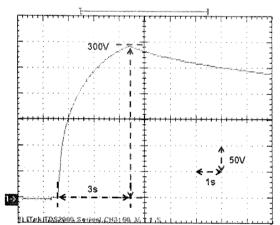

The chip is fabricated in a 1-poly 4-metal 0.35-μm high voltage CMOS process. Fig. 9 shows the chip microphotograph. The DMOS (Double-diffused Metal Oxide Semiconductor) is used for the power switch, and a protection circuit is designed. And it is integrated IGBT driver to drive of an IGBT for ramp trigger circuit. Fig. 10 shows the experimental circuit for testing the proposed architecture. And Fig. 11 shows the implemented test board. A TTRN-060S-015 transformer made by Tokyo Coil Engineering Company is used. This transformer turns ratio is 10 and L<sub>Primary</sub> is 14μH. Fig. 12 is the Experimental results of V<sub>OUT</sub> at 3.3V V<sub>BATT</sub>, 1.2A I<sub>LIM</sub> by the Tektronix TDS2024 analog oscilloscope. The vertical axis is 50V per division and the horizontal axis is 1s per division. Table 1 shows the performance of the proposed photoflash capacitor charger.

Fig. 9. Microphotograph of proposed photoflash capacitor charger.

Fig. 10. Experimental circuit for testing proposed architecture

Fig. 11. Proposed photoflash capacitor charger test board

Fig. 12. Experimental results of  $V_{OUT}\ @\ 3.3V\ V_{BATT},\ 1.2A$   $I_{LIM}$

Table 1. Performance summary

|                                     |                  | Conventio<br>nal [6] | Proposed | Units |

|-------------------------------------|------------------|----------------------|----------|-------|

| Supply voltage (V <sub>BATT</sub> ) |                  | 3.0 ~ 5.5            | 3.0~ 5.5 | v     |

| Su<br>pp<br>ly<br>cu<br>rr<br>ent   | Charging         | 5                    | 4.8      | mA    |

|                                     | Charging<br>done | 1                    | 1        | μА    |

|                                     | Shutdown         | 0.01                 | 0.01     | μА    |

| SW Maximum<br>Off-time              |                  | 18                   | 1        | μs    |

| SW Maximum<br>On-time                                            | 18               | 4         | μs |

|------------------------------------------------------------------|------------------|-----------|----|

| $I_{LIM}$                                                        | 1.0, 1.2,<br>1.4 | 0.4 ~ 1.6 | A  |

| Charging time<br>to 300V<br>@ 3.3V Vdd,<br>1.2A I <sub>LIM</sub> | 3.8              | 3         | S  |

| Efficiency                                                       | > 75             | > 75      | %  |

| Area                                                             | 2.23 x<br>1.64   | 1.6 x 1.3 | mm |

## 5. Conclusion

In this paper, the photoflash capacitor charger that has faster charging time with high efficiency by proposed control logic block is designed, simulated, and fabricated. And the proposed wide range current limiter has an advantage that user can adjust current limiting value for user convenience between charging time and battery life. The proposed photoflash capacitor charger has 3s charging time at 3.3V battery voltage, 1.2A current limit condition. It is well-suited for portable device application such as digital camera, digital video camera, and mobile phone with camera.

#### References

- [1] N. O. Sokal and R Redl, "Control Algorithms and Circuit Designs for Optimal Flyback-Charging of Energy-Storage Capacitor (e.g., for Flash Lamp or Defibrillator)," *IEEE Transactions on Power Electronics*, vol. 12 No. 5, September 1997, pp. 885-894.

- [2] Radek Nalepa, Noel Barry, Peter Meaney, "Primary Side Control Circuit of a Flyback Converter," Applied Power Electronics Conference and Exposition, 2001. APEC 2001. Sixteenth Annual IEEE, vol. 1, March 2001, pp. 542 – 547.

- [3] Mark Telefus, Anatoly Shteynberg, Mehdi Ferdowsi, and Ali Emadi, "Pulse Train Control Technique for Flyback Converter," *IEEE Transactions on Power electronics*, vol. 19, No. 3, May 2004, pp. 757-764.

- [4] S. Kaboli, S. M. R. Sadriyeh, A. Mohammadi, M. R. Zolghadri, and A. Emadi, "Application of Packet Control Method for a High Power High Voltage Flyback Converter to Reduce Noise Influence," Power Electronics and Applications, European Conference, September 2005.

- [5] Texas Instruments, "Design for Integrated Photo flash Charger and IGBT Driver," Application Note No. SLVA197, 2005, pp. 4-5, 11-13.

- [6] Allegro MicroSystems. Inc., "Photoflash Capacitor Charger with IGBT Driver," Catalog No. A8436, 2006.

- [7] Ned Mohan, Tore M. Undeland and William P. Robbins, *Power Electronics*, Wiley, 2003. pp. 342.

- [8] Behzad Razavi, Design of Analog CMOS Integrated Circuits, McGRAW-HILL press, 2001

- [9] R. Jacob Baker, CMOS Circuit Design, Layout, and Simulation, Wiley, 2005.

## 저 자 소 개

## Won Ho Choi (Member)

2006: BS degree in Electrical

Engineering, Korea University.

2006 ~ Now: Currently working toward

the MS degree in Electrical Engineering,

Korea University.

#### Woo Kwan Lee

2003: BS degree in Electrical Engineering, Korea University.

2006: MS degree in Electrical Engineering, Korea University.

2006 ~ Now: Currently working toward the Ph.D degree in Electrical Engineering, Korea University.

## Soo-Won Kim

1974: BS degree in Electrical Engineering, Korea University. 1976: MS degree in Electrical Engineering, Korea University. 1983: MS degree in Electrical Engineering, Texas A&M University. 1987: Ph.D degree in Electrical Engineering, Texas A&M University. 1987 ~ Now: Professor in Electrical

Engineering, Korea University